One side of a 12 cm Compact Disc stores an hour of stereo music in the form of a helical track of tiny pits and flats representing more than five billion databits.During playback, the pits scatter the light from a small semiconductor laser, the flats reflect it onto a photodetector. The data bits are recovered at a rate of 4.3 million bits/s and converted into a PCM signal from which the original audio waveform is accurately reconstructed without the degradation associated with analogue reproduction systems.

Philips ICs for Compact Disc decoders - 1982

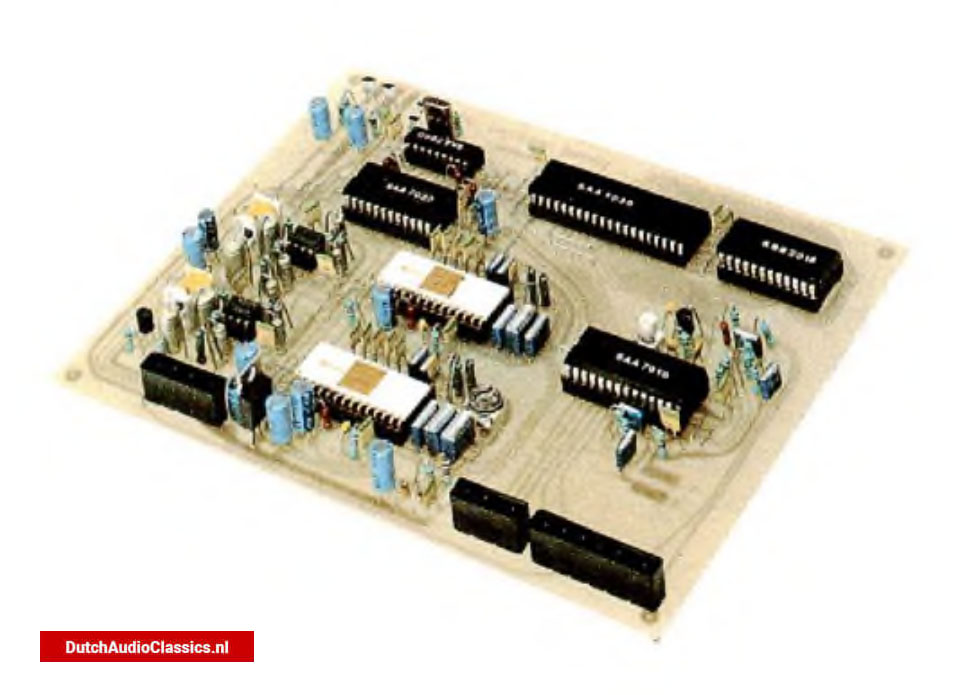

Development decoder board which performs more than 4 million decoding, control and error-correction operations every second of playback of a Compact Disc. The four new NMOS LSI circuits at the heart of this mammoth processing task enable a complete decoder controlled by one master clock to be assembled on one small single-sided board (<^220 cm2)

Development decoder board which performs more than 4 million decoding, control and error-correction operations every second of playback of a Compact Disc. The four new NMOS LSI circuits at the heart of this mammoth processing task enable a complete decoder controlled by one master clock to be assembled on one small single-sided board (<^220 cm2)

The change to digital signal processing leaves all analogue problems such as wow and flutter and crosstalk behind. Owners of a Compact Disc player will therefore be able to enjoy music of a quality unequalled by that available from disc or tape. Compact Disc players can be programmed to access individual pieces of music and reproduce them in any order desired by the listener. Some other possible features, not easily implemented in a conventional LP disc system, are the display of elapsed/remaining playing time, automatic switching of de-emphasis circuits and search and repeat functions.

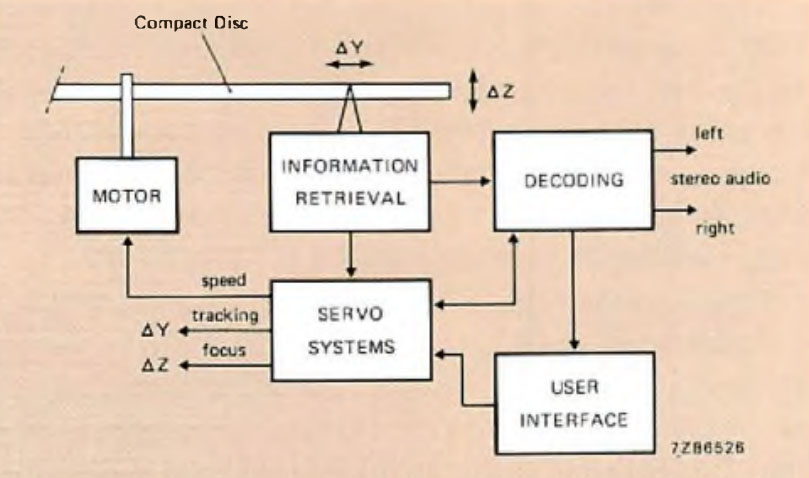

Figure 1 shows the main components of a Compact Disc player. This article describes the decoding section for which four new NMOS LSI circuits have been developed:

- SAA7010, demodulator IC (28-pin DIL).

- SAA7020, error correction IC (40-pin DIL).

- SAA7000, interpolation and muting IC (18-pin DIL).

- SAA7030, digital oversampling filter IC (24-pin DIL) used with the TDA1540 DAC (28-pin DIL) in a unique 16-bit digital-to-analogue conversion system.

Figure 1 - Functional schematic of a Compact Disc player.

Figure 1 - Functional schematic of a Compact Disc player.

These circuits are in standard DIL packages, require only a few peripheral components and are controlled by one master clock. Because of a high degree of integration, a complete decoder from h.f. input to audio output can be built on one small (≈220 cm2) single-sided printed circuit board.

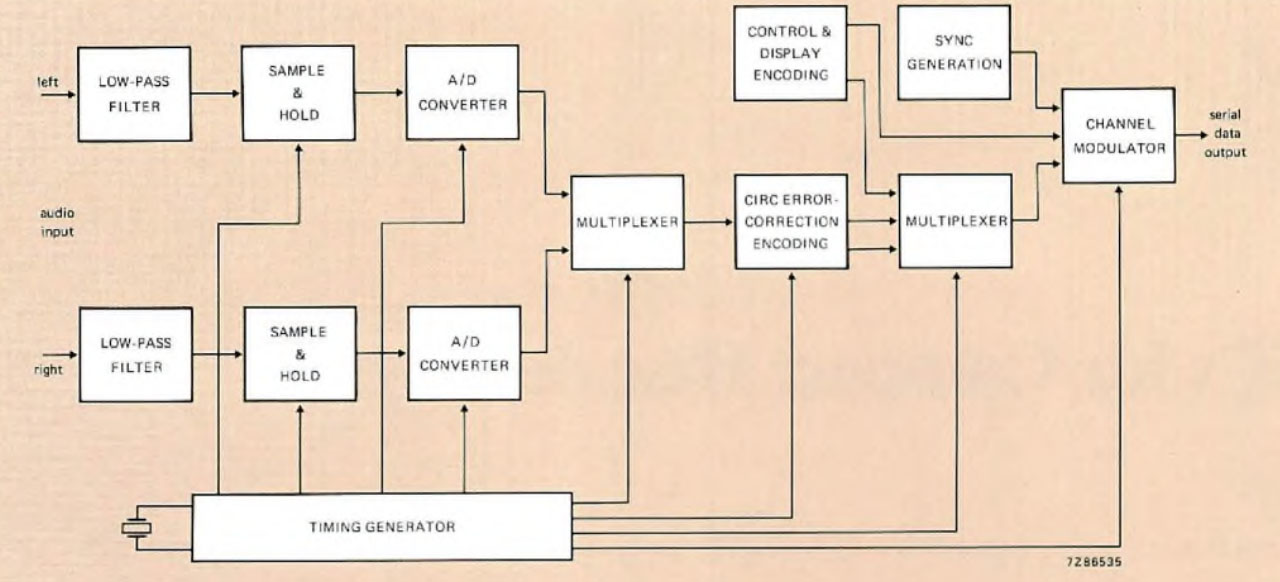

The ICs are key components determining the performance of a Compact Disc player. Before describing them and the decoding process, it will be helpful to describe briefly the digitising and encoding of audio signals onto a Compact Disc. Figure 2 shows the encoding process.

Figure 2 - Compact Disc encoding system

Figure 2 - Compact Disc encoding system

Encoding the digital audio

The first step is to sample the analogue audio and convert the samples to 16-bit PCM signals. Since the frequency spectrum of impulse-sampled audio signals is simply double sidebands of the audio signal spectrum repeated at multiples of the sampling frequency, the analogue input signals are first passed through a low-pass filter with sharp cut-off which limits their bandwidth to less than half the sampling frequency. This prevents intermodulation distortion due to aliasing. If required, the filtered analogue signals can be passed through a pre-emphasis network to improve signal-to-noise ratio (SNR).

The analogue signals are sampled at 44.1 kHz. The output of the sample and hold circuit is a flat-top PAM signal, whose pulse heights correspond to the audio signal amplitudes at the sampling instants.

Each sample is held long enough for the previous one to be converted to a 16-bit 2's complement number by an analogue-to-digital converter (ADC). 16-bit quantisation gives extremely high resolution, the maximum SNR of a 16-bit PCM signal being ≈98 dB (6n + 1.8 dB, where n is the number of bits used to express each quantisation level).

Channel separation in Compact Disc digital audio is almost total, because the data of the left channel are completely independent of those of the right.

The 16-bit binary words from the ADC go to a multiplexer which sends a serial data stream of alternately 16 left channel bits and 16 right channel bits to an error-correction encoder.

Sixteen-bit quantisation solves one problem associated with any digital audio system — quantisation noise. Another — drop-out (the loss of single or several data bits in the recovered data) — is overcome in the Compact Disc system by the method used for encoding the digital data prior to recording the Disc. This enables any errors in the signal read from a Compact Disc, which could cause distortion, to be detected and corrected during playback. A powerful multiple-eiror-correcting code called the Cross Interleave Reed-Solomon Code (CIRC) is used. This code is based on parity bits and an interleaving (rearranging) of the digital audio samples in time.

This code can correct a drop-out in which up to about 3500 successive bits are lost (equivalent to a track length on the disc of about 2.4 mm). Beyond this, it enables the loss of up to about 12 000 bits, occupying a track length of 8.5 mm, to be compensated by interpolation. This, plus the track being beneath a protective layer, is why a Compact Disc is insensitive to scratches and dirt on its surface.

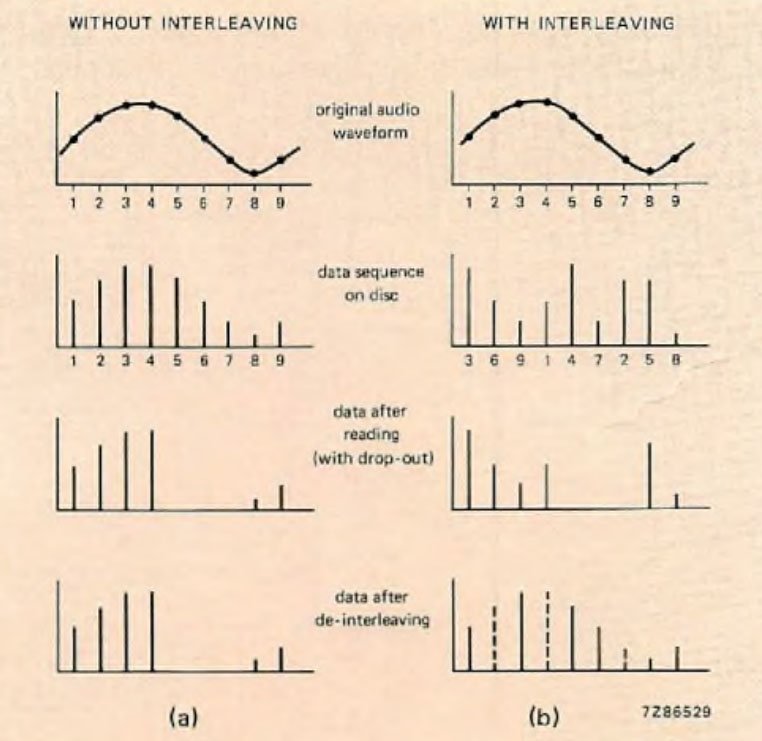

Figure 3 shows the principle of interleaving. In Fig.3(a), a sequence of signal processing events is shown without interleaving. An audio signal is sampled at instants 1, 2, 3 etc., digitised and the data representing the samples recorded onto disc. If there is a drop-out while reading the disc, some words will be missing in the received data. In Fig.3(a), three words are missing. If the length of the drop-out region is greater than the error correction ability of the decoder, the missing values cannot be reconstructed and the audio output has to be muted in order to avoid audible clicks in the reproduced sound.

In Fig.3(b), the same sequence of events is shown, this time with interleaving of data. The original audio signal is sampled, but the sequence of the samples is then rearranged prior to recording on disc. For the same drop-out as before, three words are again missing. After the original sequence of tire data words is restored, the drop-out region is spread out in time, but now there are only single errors (dashed lines) which can be easily corrected.

The Compact Disc system enables many features, not possible with the microgroove record system, to be incorporated in the new players. For example, signals can be added to mark the pause between two successive pieces of music and used to implement search and repeat functions, or to indicate remaining/elapsed playing time, titles and composers. This control and display information (known as subcoding information) must be inaudible and so is encoded separately by the control and display encoder. The 8-bit output of tins encoder means eight information channels can be recorded. Since the subcoding information is generated and recorded bit-serially, there must be provision for recognising the beginning of a block of subcoding data. There are two outputs from the encoder, one carrying the data, the other synchronising the data blocks.

The sub coding data and the 8-bit serial words from the error correction and encoding unit, which are either data or parity words, pass through a multiplexer to the channel modulator. The sync generator creates a unique pattern, not contained in the normal data, which identifies the beginning of each frame of data.

Figure 3 - Principle of interleaving

Figure 3 - Principle of interleaving

The output data of both the error correction encoding unit and the control and display encoding unit are in nonretum-to-zero (NRZ) format. Data in NRZ format are not suitable for recording onto disc, because the bit clock cannot be recovered from the data stream during playback. In addition, the data stream may contain low-frequency components which could interfere with the servo systems in the player, controlling the disc rotation and the tracking/ focusing of the laser pick-up. The NRZ data is converted to another code in the channel modulator, whose output is then recorded on disc.

The requirements of a code for an optical audio disc system are:

- bit clock can be regenerated from the data

- low spectral power at low frequencies

- permits read-out at high information density

- small error propagation.

The encoding procedure used is called Eight-to-Fourteen Modulation (EFM). As the name implies, each group of 8 data bits (called a symbol) from the error correction encoder, or from the control and display encoding unit, is encoded into a group of 14 bits. To ensure that the bit clock can be regenerated from the data, and to permit the reading of high-density information, there are always at least two 0s between successive Is and no more than ten consecutive 0s in a 14-bit EFM word. The transmitted information is contained in the transitions which are indicated by the Is. There are 277 combinations of 14 bits which satisfy the constraint of at least two 0s. Deleting the 21 patterns with ten or more 0s in a row leaves 256 combinations, which gives a one-to-one correspondence between 8-bit NRZ data and 14-bit EFM data. Code conversion can therefore be done easily, via a T flip-flop, using a look-up table stored in a ROM.

The 14-bit blocks generated cannot, however, be concatenated without violating the constraint of the two to ten Os at the block boundaries. Therefore, three merging bits are inserted between successive 14-bit blocks. These bits do not contain audio or control/display information and are skipped by the decoder. The d.c. content of the bit stream can be controlled by inserting a transition in the merging bits, if the constraints are not violated. The decision to insert is made using advance knowledge of symbols.

Because of the requirement for regenerating the bit clock, synchronisation is necessary. This is achieved by dividing the bit stream into frames and adding a unique pattern to each. Each frame contains:

- a synchronisation pattern

- twelve 16-bit data words representing 6 stereo samples

- four 16-bit error correction parity words

- one 8-bit control and display word.

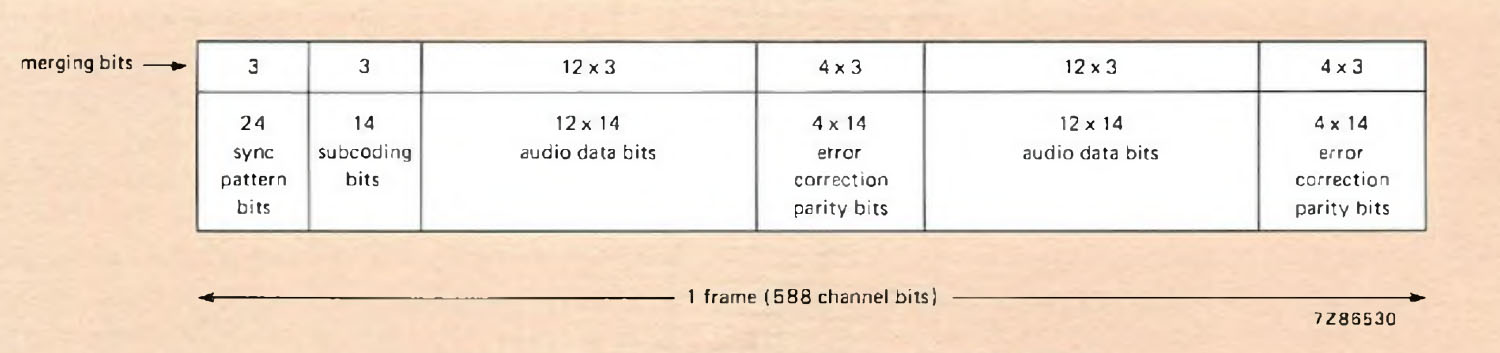

Figure 4 - Data stream after Eight-to-Fourteen Modulation (EFM)

Figure 4 - Data stream after Eight-to-Fourteen Modulation (EFM)

The 16-bit data and parity words are split into 8-bit words before EFM encoding.

The total number of channel bits per frame after encoding is 588, comprising:

- 24 sync pattern bits

- 336(12 X 2 X 14) data bits

- 112 (4 x 2 x 14) error correction bits

- 14 control and display bits

- 102 (34 x 3) merging and d.c. control bits

Figure 4 shows the arrangement of the bit stream after EFM.

Since EFM is based upon a block structure of 8-bit input data, it is well suited for the CIRC error correction system, also based on blocks of eight consecutive data bits. Propagation of errors is limited to the eight bits in a symbol.

Decorder

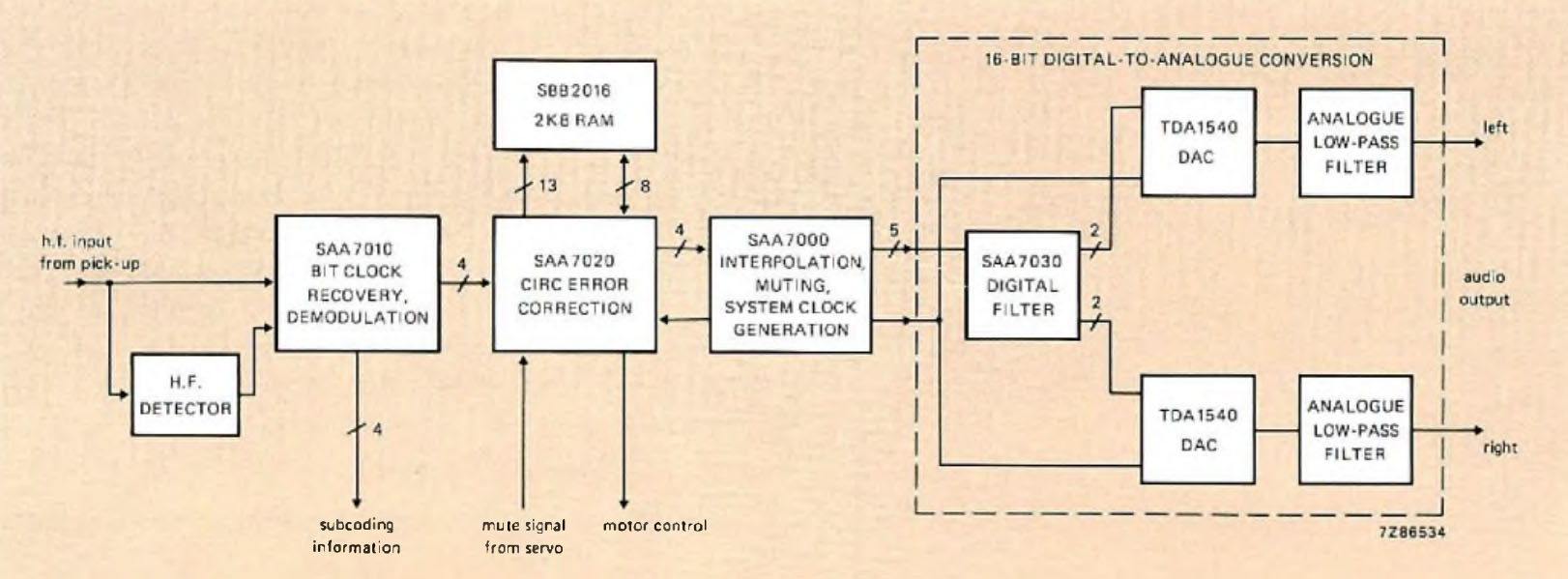

The function of tire decoding system of a Compact Disc player is to regenerate both analogue audio channels from the h.f. data stream retrieved from the disc by the laser pick-up. Figure 5 shows the block diagram of a decoder and the ICs used:

- Philips SAA7010,for thesignal processing tasks of demodulation. Converts the data stream from the laser pick-up back to its original format, regenerates the bit clock from the data stream, and separates the data representing the recorded sound from control and display data.

- Philips SAA7020 and an SBB2016 RAM. De-interleave the demodulated data from the Philips SAA7010, and detect and correct errors in the data stream. The SAA7020 generates an unreliable data signal if it is unable to correct an error. The SAA7020 also removes jitter in the data by resynchronising the data to a clock derived from a crystal oscillator.

- Philips SAA7000, for interpolation and muting. Reconstructs audio data by interpolation should the Philips SAA7020 be unable to correct any single samples in error; mutes consecutive erroneous samples.

- Philips SAA7030 and two TDA1540s for digital-to-analogue conversion. SAA7030 increases the SNR of the 16-bit data stream containing the audio information by 13dB so that 14-bit DACs can be used with no loss of quality in the reproduced audio.

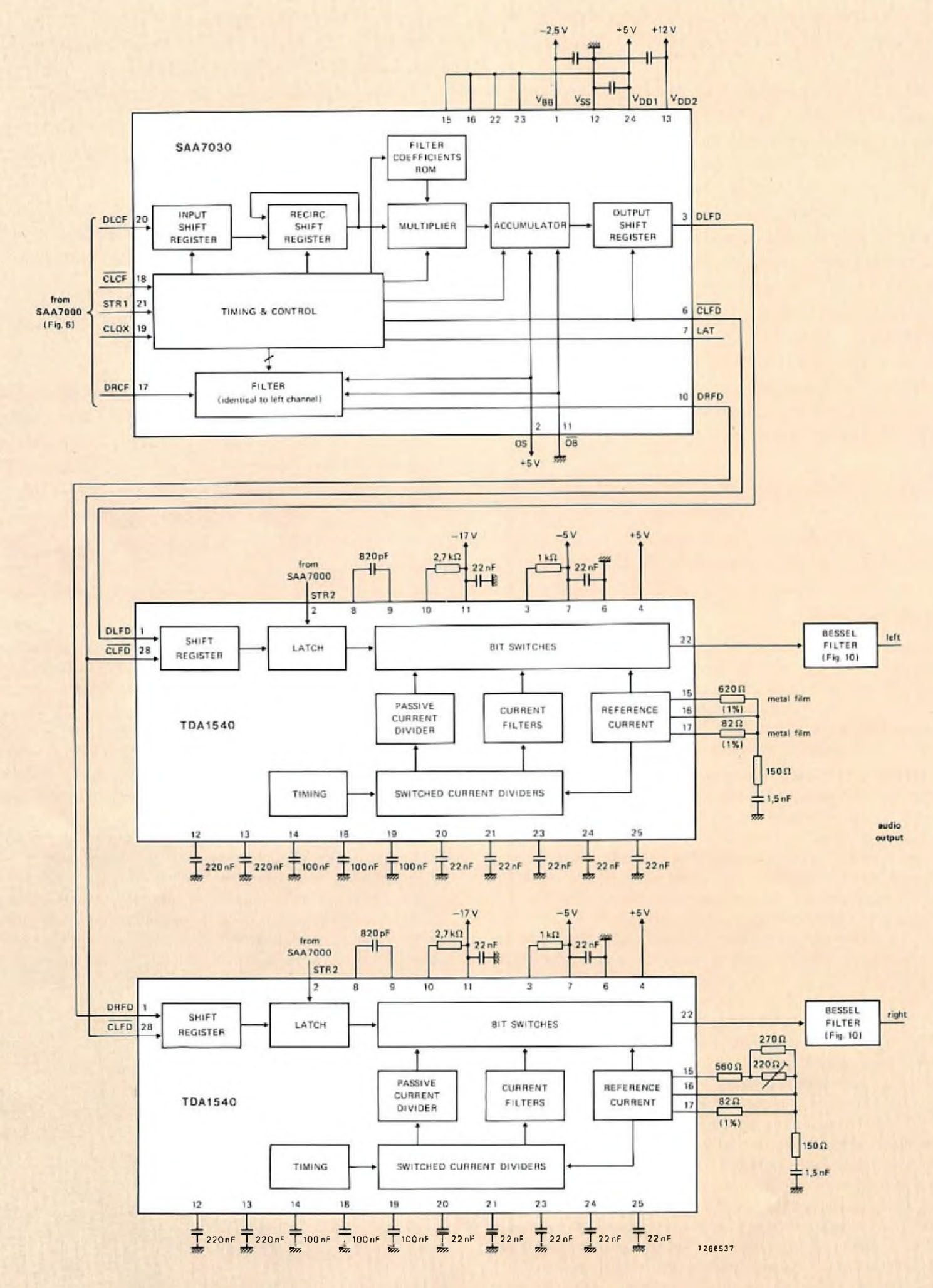

Figure 6 shows the demodulation, error correction and muting section of the decoder in more detail. Figure 8 shows the 16-bit digital-to-analogue conversion section

Figure 5 - Block diagram of a Compact Disc decoder

Figure 5 - Block diagram of a Compact Disc decoder

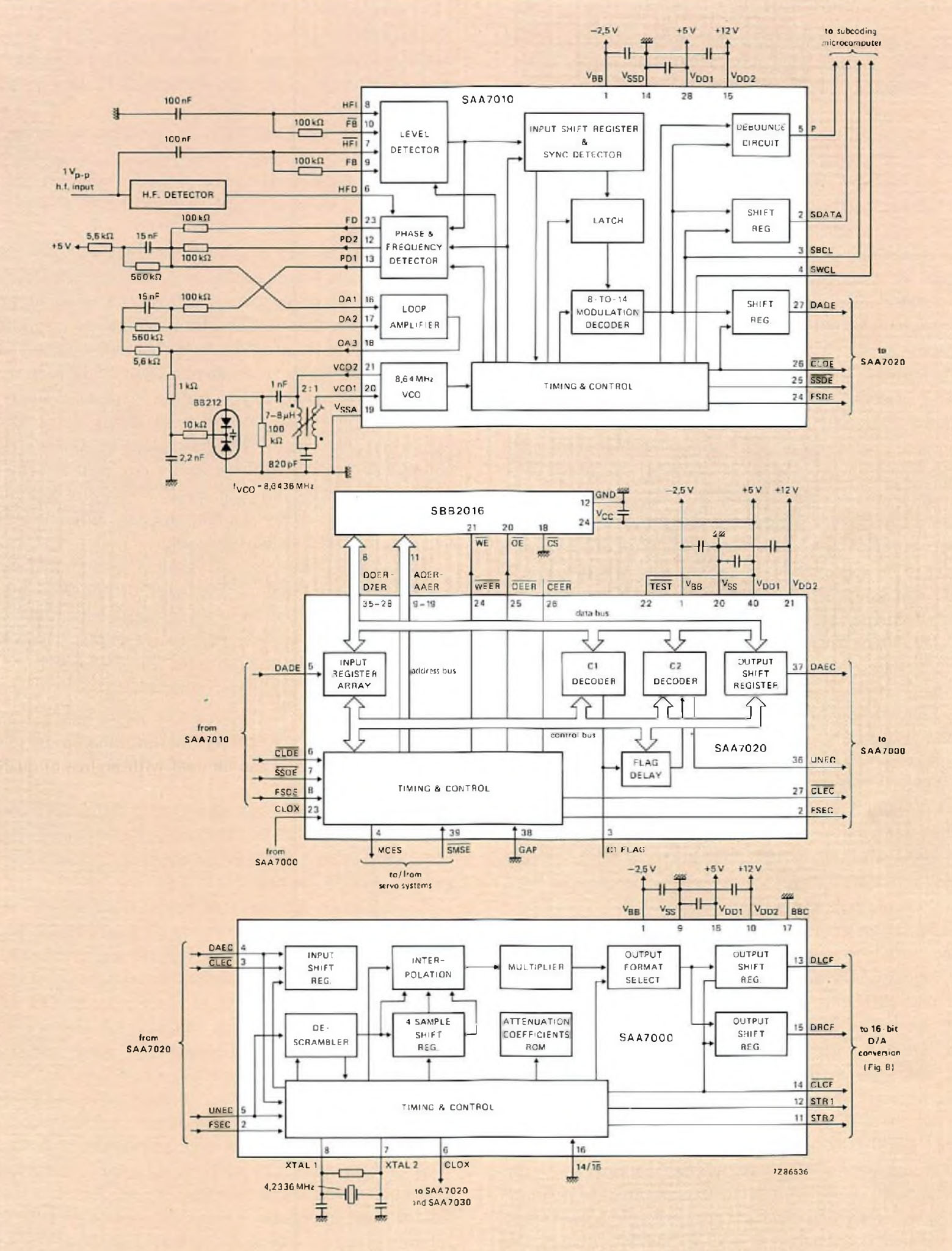

Figure 6 - Demodulation, error correction and muting section of a Compact Disc decoder

Figure 6 - Demodulation, error correction and muting section of a Compact Disc decoder

Philips SAA7010: demodulator IC

The SAA7010 forms the front-end of the decoding system and supplies demodulated data and timing signals to the error correction IC (SAA7020) and to the subcoding microcomputer.

The h.f. signal read from the Compact Disc by the laser pick-up is first amplified and filtered, then supplied to the input of the SAA7010 and to an optional h.f. threshold detector. The analogue h.f. signal is first digitised by a level detector and then passed to a phase-locked loop (PLL) which regenerates the bit clock from the incoming data.

There are six complete stereo audio samples in one frame (588 EFM channel bits) of the disc data. Therefore, one stereo sample comprises 98 channel bits. For a sampling frequency of 44.1 kHz, the data rate of the h.f. signal is 4.3218 Mbits/s. The voltage-controlled oscillator (VCO) of the PLL operates at twice the incoming data rate from which a 4.3218 MHz master clock signal used in all internal timing is derived. Frequency-sensitive and phase-sensitive detectors provide the coarse and fine tuning signals for theVCO. Both detectors are enabled/disabled using the HFD input.

The incoming data is clocked into a shift register and the sync pattern detected, which enables the start of each frame of data to be identified. Sync information is passed to the timing and control logic in order to synchronise the demodulation with the incoming data. The level detector has feedback which automatically adjusts to the optimum switching level. However, if the frequency of the incoming data falls below a set level, e.g. owing to a drop-out, the level detector switches to a nominal feedback level of half the supply voltage VDD1. This prevents the switching level drifting away from its optimum.

Provided the timing generator is locked to the h.f. signal, each 14-bit word received is stored in a latch, then converted into an 8-bit word by the EFM decoder.

In the SAA7010, a logic array is used for code conversion, not a ROM look-up table as mentioned earlier. This saves chip area and reduces power dissipation.

Demodulated audio data are shifted out of the SAA7010 to the error correction IC SAA7020 on DADE, with the clock signal CLDE and the symbol and frame sync signals SSDE and FSDE respectively.

The seven bits Q to W ofthe subcoding data plus a sync bit are shifted out serially at the SDATA output with clock SBCL and sync signal SWCL, while channel P (pause bit) is output at P after passing through a debounce circuit.

Note, use of an h.f. threshold detector at the input HFD of the SAA7010 is optional. If one is not used, the HFD input is connected to Vqq j for normal operation of the demodulator. Using an h.f. detector can improve the performance of a Compact Disc player because it disables the phase and frequency detectors in the demodulator when the amplitude of the h.f. input is small. Thus, the PLL cannot lock onto noise in the absence of an h.f. signal and so clock jitter is prevented

Philips SAA7020: Error correction IC

The SAA7020 detects, and where possible corrects, errors in the demodulated data stream and supplies these data together with a flag, indicating whether the data are correct or unreliable, to the SAA7000.

Data from the SAA7010 are arranged in frames of thirty-two 8-bit symbols. Twenty-four of these symbols contain 12 audio samples (i.e. 6 stereo samples), the remaining eight are parity symbols added for error detection and correction

Data enter serially into a register array at DADE. This array comprises a shift register which accumulates symbols for parallel processing and a FIFO register which acts as a jitter reduction circuit. The FIFO register can compensate for deviation of up to +2.25 frames from the nominal data rate. It is this register that eliminates wow and flutter in the Compact Disc system. The output data rate from the SAA7020 depends only on the clock signal CLOX derived from a crystal oscillator. Any discrepancy between the clock derived in the demodulator and that from the crystal oscillator generates an error signal MCES which controls the speed of the motor spinning the disc. MCES is a PWM signal with a range of 142 linear steps.

The CIRC makes use of interleaving and two Reed-Solomon codes Cl and C2. The data from the demodulator are de-interleaved by temporarily storing the thirty-two 8-bit symbols forming the input word of the C1 decoder and the output word of this decoder in a 2K8 RAM.

An 8-bit bidirectional bus is used for transferring data to and from the RAM, an 11 -bit bus for addressing. Three bits control the RAM: write enable WEER, output enable OEER, and chip enable CEER. The last is for operation with pseudo-static RAMs.

The Cl decoder of the SAA7020 is designed to correct one erroneous symbol in a 32-symbol frame. The C2 decoder is designed to correct one erroneous symbol, or two erasures in a group of 28 symbols.

The input word to the Cl decoder is checked for errors by multiplying this word with the Cl parity check matrix. This produces four syndromes. If there are no errors in the input word, all four syndromes are equal to zero and the 28 data symbols at the output of the Cl decoder (4 parity symbols being discarded) are written back into the RAM unchanged. In case of one erroneous symbol, this is corrected and the 28 corrected output symbols are written into the RAM. In case of two or more erroneous symbols, the 28 output symbols are written into the RAM unchanged and a flag is set which marks these 28 symbols as unreliable.

Since each symbol in a Cl output word is delayed by a different amount before reaching the C2 decoder, the Cl flag of each unreliable symbol is delayed by the same amount as the symbol to ensure that symbol and flag arrive at the input of the C2 decoder together.

The output symbols of the Cl decoder are de-interleaved further by means of the RAM. Then, the 28 symbols forming the input word of the C2 decoder are also checked for errors by examining the four syndromes resulting from multiplication of this word with the C2 decoder parity check matrix.

If there are no errors, all four syndromes are equal to zero, and the 24 data symbols at the output of the C2 decoder are written back into the RAM unchanged and the remaining four parity symbols discarded.

In case of one erroneous symbol, this symbol is corrected in the same way as for the Cl decoder. Then, the corrected 24 output symbols 'are written into the RAM. In case of two erroneous symbols, the sum of the error values is given by one of the syndromes. Information about the position of erasure symbols is given by the flags. With this additional information, both symbols can be corrected and tire 24 corrected output symbols are written back into the RAM. In case of more than two erroneous symbols in a C2 word, all 24 symbols are rewritten into the RAM unchanged and a C2 flag is set which marks these 24 symbols as unreliable.

Data from die SAA7020 are output on DAEC in 16-bit: bursts separated by 8-bit intervals. If the unreliable data signal UNEC is output simultaneously with a data symbol, it marks that symbol as unreliable. If UNEC is output during the interval between data bursts, it indicates that the sample arriving 30 sampling periods later is unreliable. This advance information of the reliability ofsymbols is used in the SAA7000 in a muting procedure.

The unreliable data signal is generated when:

- both Cl and C2 decoders detect an uncorrectable error pattern. In this case, UNEC marks one or more symbols of the C2 output data as unreliable.

- Cl fails to detect an error, but C2 detects it without being able to correct all erroneous symbols. In this case, the whole C2 output frame is marked unreliable.

- a mute signal SMSE is received from the servo system. UNEC is immediately activated and marks symbols as unreliable as long as SMSE is present.

The output data are shifted out serially with the data clock CLEC and the frame sync signal FSEC. The logic state of DAEC in the gaps between successive clock bursts, which is determined by the input GAP, is used to select 2’s complement or offset binary format for the SAA7000.

The 8-bit input and output data format of the SAA7020 makes it also suitable for error correction in other applications.

CIRC decoding

Use of error correction is one of the fundamental reasons why digital audio is vastly superior to analogue audio. And from a practical point ot view, the ability to correct errors means that the requirements for disc manufacture are not pushed to impossible limits.

A very powerful error-correcting code called the Cross interleave Reed-Solomon Code is used in the Compact Disc system. This code, which is based on the use of parity bits and an interleaving of the digital audio samples, enables an error burst of up to about 3500 bits to be corrected. Beyond this, it enables a loss of up to about 12 000 bits to be compensated by interpolation. In systems not using interleaving, a drop-out means that several adjacent samples are lost, leaving no chance of reconstructing them.

Two Reed-Solomon Codes termed C1 and C2 are used for correcting erroneous audio samples. C1 is characterised by thirty-two 8-bit symbols, comprising 28 data symbols and 4 parity symbols, C2 is characterised by twenty-eight 8-bit symbols, comprising 24 data symbols and 4 parity symbols. The minimum distance of each code, i.e. the Hamming distance at symbol level, is five. Thus, in theory, 2 symbols in error, or four erasures (symbols whose position is known but whose value is not) can be corrected

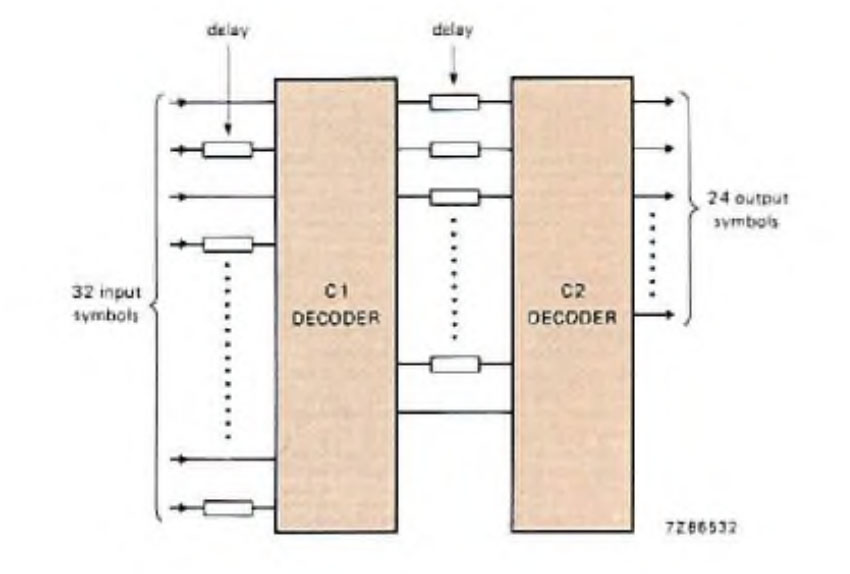

Figure 7 shows the principle of a CIRC decoder. Delays are used to rearrange (de-interleave) the digital samples back to their original sequence and are organised for efficient error correction.

Delays at the input of the C1 decoder are all of equal length and separate the even and odd numbered symbols. This enables the C1 decoder to correct small errors in adjoining symbols. Delays between the two decoders are of unequal length and longer than those at the input of the C1 decoder which enables the C2 decoder to correct burst errors.

The input to the Cl decoder is a frame of 32 symbols which is multiplied by the C1 parity check matrix to produce four syndromes. From the syndromes, errors can be detected and corrected. The C1 decoder of the SAA7020 is designed to fully correct one erroneous symbol out of a 32-symbol frame. If there is more than one error, each of the 28 output symbols (the four Cl parity symbols having been dropped) is marked with a flag, indicating that each may contain an error. If there is no flag associated with a symbol arriving at the C2 decoder, that symbol is correct

The C2 decoder is designed to correct one erroneous symbol, or two erasures. When even the C2 decoder cannot correct all errors, it outputs the 24 data symbols (the four C2 parity symbols having been dropped) uncorrected, but marked with flags. Most of these output symbols are usually error-free and can be reconstructed by linear interpolation, because the combination of the C1 and C2 flags is used as an unreliable data signal for interpolation, or if necessary, muting of symbols in the SAA7000.

Figure 7 - Principle of a CIRC decoder

Figure 7 - Principle of a CIRC decoder

Figure 8 - 16-bit digital-to-analogue conversion section of a Compact Disc decoder

Figure 8 - 16-bit digital-to-analogue conversion section of a Compact Disc decoder

Philips SAA7000: Interpolation and muting IC

The SAA7000 eliminates the audible annoyance that could result if an erroneous symbol which managed to get through the error correction circuitry was processed further. The SAA7000 also generates the clock used for internal timing of the SAA7020 and SAA7030.

Serial data from the SAA7020 on DAEC are entered into a shift register using the clock CLEC. Data are then descrambled and separated into left and right channel samples. A similar descrambling and separation is performed on the unreliable data flag UNEC. When there are no unreliable data flags, the data values of the audio samples are unaffected by the SAA7000.

When, for either left or right channel, a single unreliable sample is flagged between two correct samples, linear interpolation is used to replace the erroneous sample. If two or more adjacent samples are flagged as unreliable, they are muted. Starting thirty samples before muting (by making use of the advance information of UNEC), the correct samples are attenuated smoothly to zero according to a cosine curve. The levels of the first thirty samples following muting are then increased back to the normal level, again according to a cosine curve. The thirty-sample (5-frame) delay necessary in muting is obtained using the 2K8 RAM.

The data which are now either correct or processed are converted into 2’s complement or offset binary depending on the digital-to-analogue converters used. Selection is made by the status of DAEC during the intervals between input samples which is controlled by the GAP input of the SAA7020. Left and right channel output data on DLCF and DRCF are clocked out by the shift clock CLCF. Strobe signals STR1 and STR2 are generated for the digital-toanalogue conversion unit. A 14-bit or 16-bit output data format can be selected using the input 14/16. A full-performance 16-bit conversion system is described in the next section.

A crystal oscillator is used to generate internal timing signals and the clock signal CLOX for the SAA7020 and the SAA7030. By using the frame sync signal FSEC to reset the internal timing, the SAA7000 is automatically synchronised with the output of the SAA7020.

16-bit digital-to-analogue conversion

The digital-to-analogue conversion section (Fig.8) converts the digital output data from the interpolation and muting IC to analogue voltages and removes all unwanted frequency components above the audio band.

This conversion system is an outstanding feature of the Compact Disc decoder. It is based on a digital oversampling filter (SAA7030) followed by two (one for each channel) 14-bit DACs (TDA 1540) and low-order analogue filters. This arrangement has the SNR of a system using 16-bit DACs and high-order filters, plus the following advantages over that approach:

- linear phase response in the audio band (0—20 kHz)

- reduced slew rate distortion

- requires only a 14-bit DAC

- less intermodulation distortion, because the oversampling frequency moves any intermodulation products well outside the audio band

- only a simple low-cost analogue filter is needed after the DAC to suppress any residual frequency components

Philips SAA7030: digital oversampling filter IC

The SAA7030 consists of three main parts: oversampling section, transversal filter, and noise shaper. Circuitry in the SAA7030 is duplicated, one for each channel.

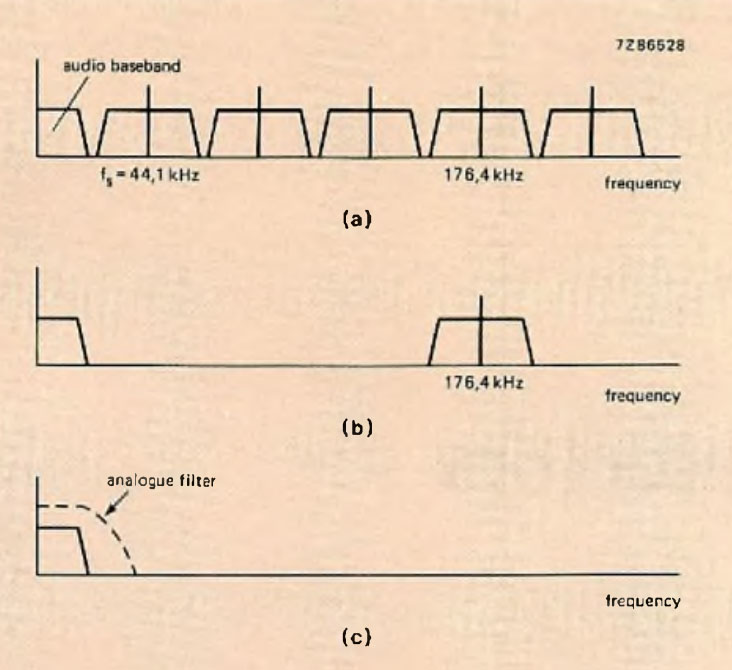

The two 16-bit data streams, at DLCF and DRCF are fed into shift registers which quadruple the sampling frequency from 44.1kHz up to 176.4kHz. Quadrupling the sampling frequency also quadruples the effective audio bandwidth, which is thus increased from 22 kHz to 88 kHz. The quantisation noise power, previously distributed uniformly across a 22kHz bandwidth, is now distributed uniformly up to 88 kHz. Since 75% of the noise is now above the audio band, it can be suppressed by filtering.

The SAA7030 incorporates two identical filters, one for each stereo channel. Each filter is a finite impulse response transversal filter of length 24 with ninety-six 12-bit coefficients and using 16-bit input data words entering at 44.1 kHz. A recirculating shift register is used to store data required during the multiplication of input data with the filter coefficients which are stored in ROM. Each multiplication produces a 28-bit word which is stored in an accumulator, the 14 most significant bits of the words are then shifted out at DLFD for the left channel, DRFD for the right channel, with the clock CLFD. Overflow protection is incorporated so that the output always limits cleanly in the unlikely event of accumulator overflow.

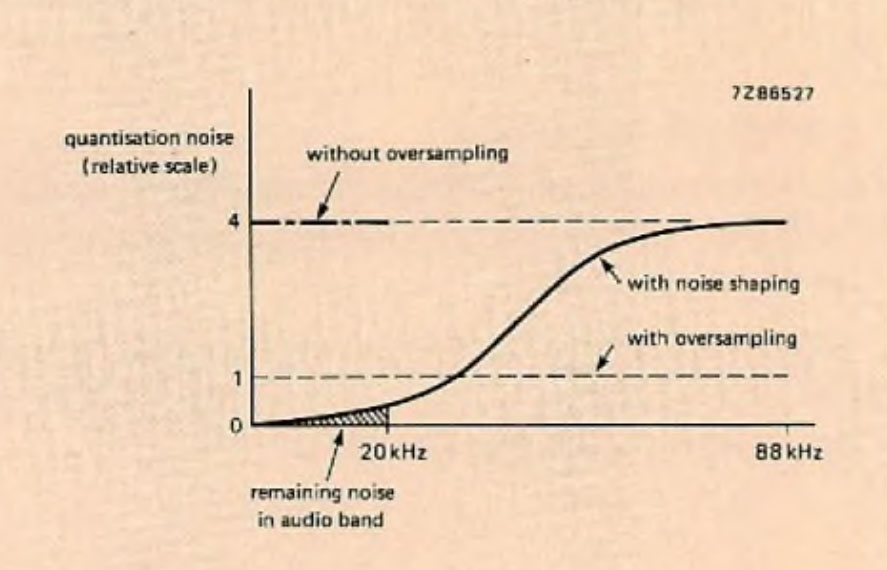

Oversampling and filtering add 6 dB to the SNR of the digital audio signal, bringing it to 90dB for the 14-bit output words. A further improvement of 7 dB is obtained in the SAA7030 by means of a noise shaper. This circuit redistributes the quantisation noise, now uniformly spread across 0-88 kHz because of oversampling, reducing the noise in the audible region still further and increasing it above 22 kHz, see Fig.9.

A choice of offset binary or 2's complement output data can be made using OB. The OS input enables a 3% d.c. offset to be added. This can be useful to reduce the effects of glitches at low output voltages with certain DACs. A 176.4 kHz strobe (LAT) is provided which can be used to latch data into the DAC in applications where a SAA7000 is not used.

Figure 9 - How 16-bit SNR is obtained from a system using 14-bit DACs. Oversampling reduces the in-band quantisation noise by spreading the total noise over a wide bandwidth. Only a quarter of the original quantisation noise remains in the audio band after oversampling. This increases the SNR of the words applied to the 14-bit DACs from 84 dB to 90 dB. Noise shaping adds another 7dB, making the maximum SNR of the conversion system 97 dB, the same as that of a conventional 16-bit system

Figure 9 - How 16-bit SNR is obtained from a system using 14-bit DACs. Oversampling reduces the in-band quantisation noise by spreading the total noise over a wide bandwidth. Only a quarter of the original quantisation noise remains in the audio band after oversampling. This increases the SNR of the words applied to the 14-bit DACs from 84 dB to 90 dB. Noise shaping adds another 7dB, making the maximum SNR of the conversion system 97 dB, the same as that of a conventional 16-bit system

Philips TDA1540: 14-bit DAC

Each TDA1540 converts 14-bit digital audio samples arriving at 176.4kHz to an analogue output current. The output current is held between conversions by latching a flip-flop in the output circuitry of the DAC.

Data DLFD (left channel), or DRFD (right channel) are entered serially with the clock CLFD. STR2 strobes the input data into a latch.

The TDA1540 uses a method of current division called dynamic element matching to achieve high-accuracy, binaryweighted currents with long-term stability. The input data, are used to activate fourteen bit switches which determine the output current. Conversion to an output voltage is done in the analogue filters following the DAC.

The hold function of the DAC results in a (sin x)/x response with a first zero point at 176.4kHz which suppresses the signal around that frequency.

If desired, one of the reference current sources in the TDA 1540s can be adjusted, see Fig.8. This will compensate for slight differences in the DAC output currents for identical input data due to tolerances in the external components.

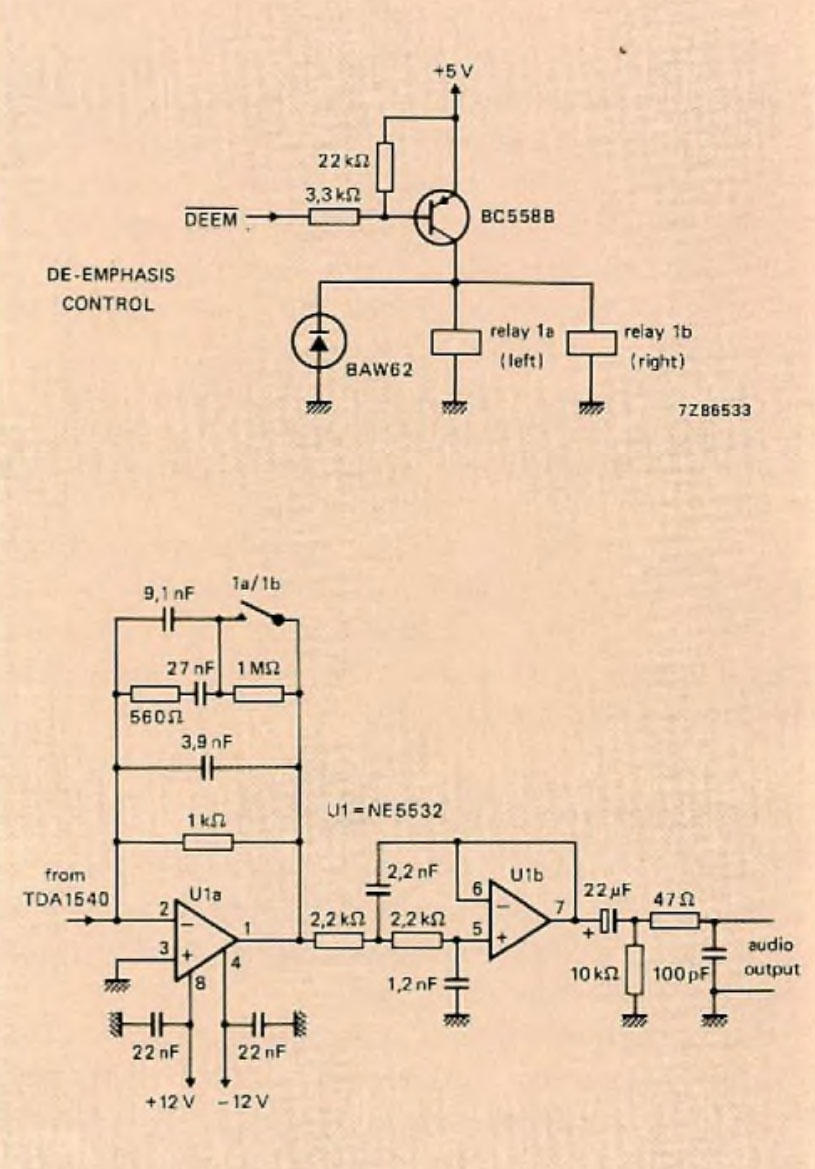

Analogue filters

The analogue filters suppress any remaining frequencies above the audio band. Since the first spectral lobe is at 176.4 kHz ± 20 kHz and has already been largely suppressed by the hold function of the DAC, third order low-pass filters provide sufficient attenuation. A Bessel filter with a cut-off frequency of 30 kHz is used because it has a linear phase characteristic. Figure 10 shows a suitable filter designed around the NE5532 dual opamp. The output of the filter is 1 V r.m.s. max. The filter components don't have to be adjusted and the de-emphasis circuit can be automatically controlled by information on the discs

Both the Bessel filter response and the (sin x)/x response of the DAC have been taken into account when calculating and scaling the filter coefficients in the SAA7030 to give the digital-to-analogue conversion unit a flat frequency response in the audio band.

Note: the conversion system can be used at other sampling frequencies since the digital filter retains its cutoff frequency at 0.45 times the input sampling frequency. In addition, the (sin x)/x compensation is unchanged for different sampling frequencies, the first zero always occurring at the oversampling frequency. For a large frequency variation, only the analogue filter has to be changed to maintain an optimally flat amplitude characteristic.

Figure 11 shows how the original audio spectrum is recovered from the digital audio by oversampling and digital filtering followed by analogue filtering.

Figure 10 - hird-order Bessel filter shown in Figure 8

Figure 10 - hird-order Bessel filter shown in Figure 8

Figure 11 - Oversampling and digital filtering remove the spectral lobes between the baseband and 176.4 ± 20 kHz, so that cheap low-order low-pass analogue filters can be used after the DACs instead of very-high-order ones necessary to suppress the 44.1 ± 20 kHz lobe in systems not using oversampling techniques. (a) Spectrum of an impulse-sampled audio signal sampled at 44.1 kHz. (b) Spectrum after oversampling at 176.4 kHz and digital filtering which suppress the lobes between the audio baseband and 176.4 ± 20 kHz. (c) Audio output spectrum. The lobe around 176.4 kHz is suppressed by the hold function of the DAC, which has a sin x/x characteristic with a first zero at 176.4 kHz, and by the analogue low-pass output filter with a cut-off frequency between 30 and 40 kHz

Figure 11 - Oversampling and digital filtering remove the spectral lobes between the baseband and 176.4 ± 20 kHz, so that cheap low-order low-pass analogue filters can be used after the DACs instead of very-high-order ones necessary to suppress the 44.1 ± 20 kHz lobe in systems not using oversampling techniques. (a) Spectrum of an impulse-sampled audio signal sampled at 44.1 kHz. (b) Spectrum after oversampling at 176.4 kHz and digital filtering which suppress the lobes between the audio baseband and 176.4 ± 20 kHz. (c) Audio output spectrum. The lobe around 176.4 kHz is suppressed by the hold function of the DAC, which has a sin x/x characteristic with a first zero at 176.4 kHz, and by the analogue low-pass output filter with a cut-off frequency between 30 and 40 kHz

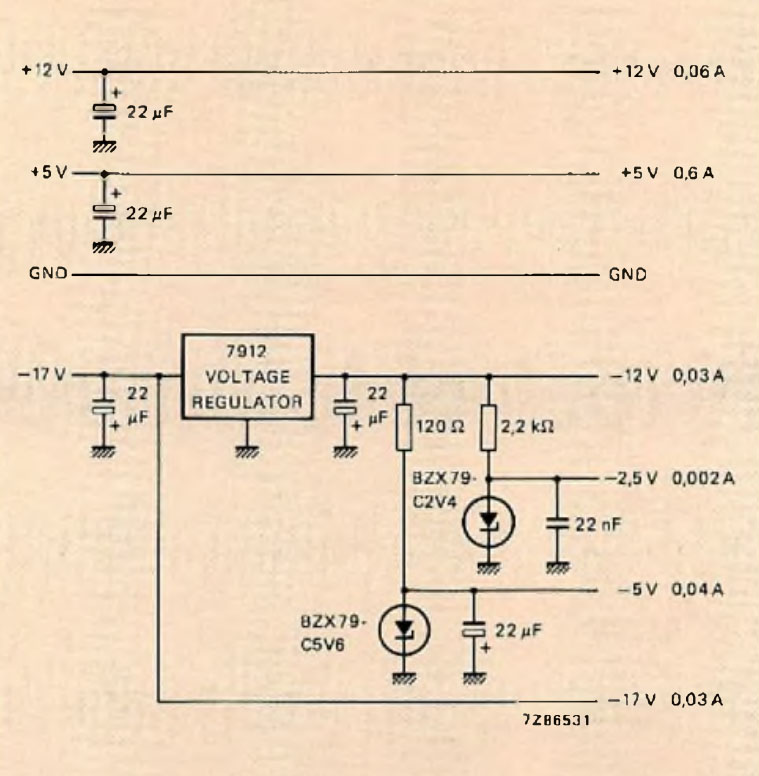

Figure 12 - Power supply of decoder

Figure 12 - Power supply of decoder

Power supply

Supplies for the decoder shown in Figs.6 and 8 are easily derived. Figure 12 shows an example

References

- VRIES, L. B, IMMINK, K. A., N1JBOER, J. G., HOEVE, H., DOI, T. T., ODAKA, K„ OGAWA, H., 'The Compact Disc Digital Audio System - Modulation and Error Correction', 67th. AES Conv., No. 1674(11-8), 1980.10.

- VAN DE PLASSCHE, R.J., 'Monolithic 14-bitDAC with 85 dB S/N ratio', Electronic Components and Applications, Vol.2, No.4, August 1980, pp. 234-241.

Source: Philips Electronics components & applications. VOL. 4 NO. 3. May 1982